# Hafnium-based High-k Gate Dielectrics

A. P. Huang<sup>1,2</sup>, Z. C. Yang<sup>1</sup> and Paul K. Chu<sup>2</sup>

<sup>1</sup>Department of Physics, Beijing University of Aeronautics and Astronautics, Beijing 100191, <sup>2</sup>Department of Physics and Materials Science, City University of Hong Kong, Tat Chee Avenue, Kowloon, Hong Kong, <sup>1</sup>Hong Kong, China <sup>2</sup>China

# 1. Introduction

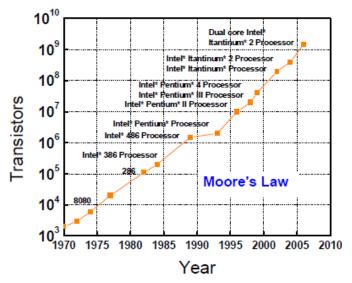

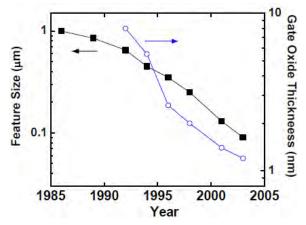

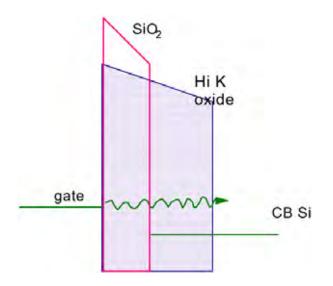

Scaling of silicon dioxide dielectrics has once been viewed as an effective approach to enhance transistor performance in complementary metal-oxide semiconductor (C-MOS) technologies as predicted by Moore's law [1]. Thus, in the past few decades, reduction in the thickness of silicon dioxide gate dielectrics has enabled increased numbers of transistors per chip with enhanced circuit functionality and performance at low costs (Fig. 1). However, as devices approach the sub-45 nm scale, the effective oxide thickness (EOT) of the traditional silicon dioxide dielectrics are required to be smaller than 1 nm, which is approximately 3 monolayers and close to the physical limit (Fig. 2), thus resulting in high gate leakage currents due to the obvious quantum tunneling effect at this scale (Fig. 3). To continue the downward scaling, dielectrics with a higher dielectric constant (high-k) are being suggested as a solution to achieve the same transistor performance while maintaining a relatively thick physical thickness [2]. Many candidates of possible high-k gate dielectrics have been suggested to replace SiO<sub>2</sub> and they include nitrided SiO<sub>2</sub>, Hf-based oxides, and Zr-based oxides. Hf-based oxides have been recently highlighted as the most suitable dielectric materials because of their comprehensive performance. One of the key issues concerning new gate dielectrics is the low crystallization temperature. Owing to this shortcoming, it is difficult to integrate them into traditional CMOS processes. To solve these problems, additional elements such as N, Si, Al, Ti, Ta and La have been incorporated into the high-k gate dielectrics, especially Hf-based oxides. In the following sections, the requirements of high-k oxides, brief history of high-k development, various candidates of high-k, and the latest hafnium-based high-k materials are discussed.

# 2. Requirements of high-k oxides

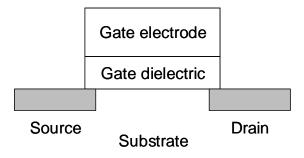

Among the various requirements of gate dielectric materials, the most important are good insulating properties and capacitance performance (Fig. 4). Because the gate dielectric materials constitute the interlayer in the gate stacks, they should also have the ability to prevent diffusion of dopants such as boron and phosphorus and have few electrical defects which often compromise the breakdown performance. Meanwhile, they must have good thermal stability, high recrystallization temperature, sound interface qualities, and so on.

Fig. 1. Enhanced Performance Trend as Predicted by Moore's Law. Processing power has steadily risen as transistors become more complex [1].

Fig. 2. Feature size of transistors downscales with time and the gate oxide thickness decreases accordingly [1].

### 2.1 K value, band gap and band offset

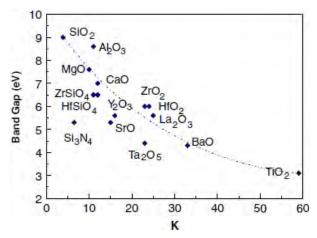

With regard to capacitance performance, the requirement is that the k value should be over 12, preferably 25–30. An appropriate k value means that the dielectrics will have a reasonable physical thickness which is enough to prevent gate leakage and not too thick to hamper physical scaling when achieving the target EOT. On the other hand, a very large k value is undesirable in CMOS design because they cause unfavorable large fringing fields at the source and drain regions [4]. Table 1 and Fig. 5 show that the k values of some oxides vary inversely with the band gap, so a relatively low k value is needed [5]. There are

Fig. 3. Schematic of direct tunneling through SiO<sub>2</sub> [3].

Fig. 4. Schematic drawing of a MOS stack.

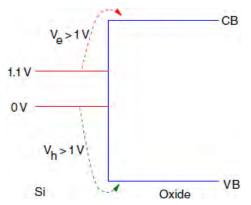

numerous oxides with extremely large k values, such as SrTiO<sub>3</sub>, which are candidates in DRAM capacitors [6], but their band gap is too small. According to the required insulating properties, the gate dielectrics must exhibit at least the band offset of 1 eV while in contact with the Si substrate in order to avoid serious gate leakage and breakdown. The band offset is required to be over 1 eV in order to inhibit conduction by the Schottky emission of electrons or holes into the oxide bands [5, 7], as schematically shown in Fig. 6. This means that the materials must have both the conduction band offset (CB) and valence band offset (VB) over 1 eV. In fact, the CB offset is less than the VB offset, which suggests oxides with band gaps wider than 5 eV may be excluded as gate dielectrics. For those oxides with narrow band gaps, either the CB offsets or the VB offsets may be smaller than 1 eV, also limiting the choice of these materials.

| Dielectric            | k    | Band gap (eV) | CB offset (eV) |

|-----------------------|------|---------------|----------------|

| Si                    | -    | 1.1           | -              |

| SiO <sub>2</sub>      | 3.9  | 9             | 3.2            |

| $Si_3N_4$             | 7    | 5.3           | 2.4            |

| $Al_2O_3$             | 9    | 8.8           | 2.8            |

| $Y_2O_3$              | 15   | 6             | 2.3            |

| $Ta_2O_5$             | 22   | 4.4           | 0.35           |

| TiO <sub>2</sub>      | 80   | 3.5           | 0              |

| $La_2O_3$             | 30   | 6             | 2.3            |

| a- LaAlO <sub>3</sub> | 30   | 5.6           | 1.8            |

| $SrTiO_3$             | 2000 | 3.2           | 0              |

| $ZrO_2$               | 25   | 5.8           | 1.5            |

| $HfO_2$               | 25   | 5.8           | 1.4            |

| HfSiO <sub>4</sub>    | 11   | 6.5           | 1.8            |

Table I. Dielectric constant (k), band gap and CB offset on Si of the candidate gate dielectrics.

Fig. 5. Static dielectric constant versus band gap for candidate gate oxides [5].

#### 2.2 Thermal stability

In present CMOS processes, the gate stacks must undergo rapid thermal annealing (RTA) of 1000 °C for 5s. This requires that the gate oxides must be thermally and chemically stable especially with the contacting materials. Thus, group II, III, IV oxides with a higher heat of formation than SiO<sub>2</sub> such as SrO, CaO, BaO, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub> and lanthanides may be useful. Additionally, group II oxides which react with water are not favorable. Therefore, from the thermal stability point of view, only Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, Sc<sub>2</sub>O<sub>3</sub> and some lanthanides such as Pr<sub>2</sub>O<sub>3</sub>, Gd<sub>2</sub>O<sub>3</sub> and Lu<sub>2</sub>O<sub>3</sub> are left [3]. However, some materials with higher heat of formation than SiO<sub>2</sub> may also be slightly reactive with Si such as ZrO<sub>2</sub>, forming the silicide, ZrSi<sub>2</sub> [8, 9]. Among these high k dielectrics, HfO<sub>2</sub> has both a high k value as well as chemical stability with water and Si.

Fig. 6. Schematic of band offsets dependence of carrier injection in oxide band states.

## 2.3 Crystallization temperature

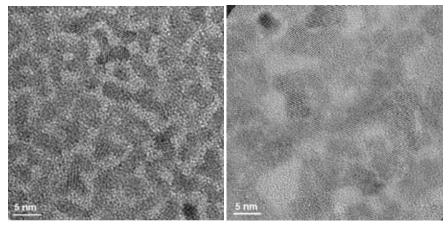

Owing to the absence of grains and good diffusion barrier properties, amorphous materials are preferred to crystalline ones. The grains which lie in the crystalline systems can often be the pathways for dopants diffusion and breakdown. Unlike SiO<sub>2</sub>, high-k oxides usually have low crystalline temperature and can easily crystallize when subjected to RTA. In particular, HfO<sub>2</sub> and ZrO<sub>2</sub> crystallize at much lower temperatures at ~400 °C and ~300 °C, respectively (Fig. 7). According to the above factors, the approach to improve the crystallization temperature of HfO<sub>2</sub> and ZrO<sub>2</sub> should be considered. The crystallized HfO<sub>2</sub> has a much lower leakage current which has convinced many companies such as Intel and Freescale to adopt binary oxides because of their relative higher k values.

Fig. 7. TEM image of crystallization in  $HfO_2/SiO_2$  dielectrics with (a) 40%  $HfO_2$  and (b) 80%  $HfO_2$  [10].

### 2.4 Interface quality

The interface between the high-k dielectrics and Si substrate must have the highest electrical quality and flatness, absence of interface defects, and low interface state density  $D_{it}$ . Bad

interface quality can cause high fixed charge density, inducing a large shift in the flat band voltage ( $V_{fb}$ ) which severely reduces the performance and reliability of the transistor. Most of the high-k materials reported in this chapter have  $D_{it} \sim 10^{11} - 10^{12} \text{ eV/cm}^2$  and also exhibit a substantial flatband voltage shift larger than 300 mV [11]. Therefore, it is crucial to improve the quality of the interface. There are two ways to ensure a high quality interface, either using a crystalline oxide grown epitaxially on the Si or an amorphous oxide. An amorphous oxide has many advantages over a poly-crystalline oxide. Firstly, it is more economically and more compatible with existing processes. Secondly, the amorphous oxide can minimize the number of interface defects. Thirdly, it is possible to gradually vary the composition of an amorphous oxide without creating a new phase, as in silicate alloys, or when adding nitrogen or other metal elements. Fourthly, an amorphous oxide and its dielectric constant are isotropic, so that fluctuations in polarization from differently oriented oxide grains will not cause scattering of carriers. Finally, amorphous phases have no grain boundaries. The advantages of epitaxial oxides may come in the future, where their more abrupt interfaces allows us to reach lower EOTs. Besides the above consideration, the configuration of interface bonding is also significant. As the  $SiO_2/Si$  interface has high quality, the ideal gate dielectric stack may well turn out to have an interface comprising several monolayers of Si-O (and possibly N) containing materials, which can be a pseudobinary layer at the channel interface. This layer can serve to preserve the critical, high-quality nature of the  $SiO_2$ interface ( $D_{it} \sim 2x10^{10} \text{ eV/cm}^2$ ) while providing a higher-k value for that thin layer. The same pseudobinary materials can also extend beyond the interface, or a different high-k material can be used on top of the interfacial layer.

### 2.5 Defects

Similar to interface defects, bulk defects formed in high-k oxides during deposition also causes degraded transistor performance due to the rising number of defect-related fixed charges. In addition, charges trapped in defects will cause a shift in the gate threshold voltage of the transistor, which is the key characteristic of performance. Furthermore, the trapped charges change with time and so the threshold voltage also shifts with time, leading to problems associated with negative bias temperature instability (NBTI) and positive bias temperature instability (PBTI). Meanwhile, trapped charges scatter carriers in the channel causing reduced carrier mobility. Lastly, they are the starting points for electrical failure and oxide breakdown. Typically, these defects are sites of excessive or deficient oxygen or

Fig. 8. Schematic diagram of two types of defects located (a) at the  $HfO_2/SiO_2$  interface and (b) in the bulk of  $HfO_2$  film.

impurities. Unfortunately, most of the high-k oxides inherently have more interface defects in contact with the Si substrate and bulk defects than SiO<sub>2</sub> because their bonding cannot relax as easily [12] (Fig. 8). Nowadays, many groups are endeavoring to reduce defect densities by either processing control or engineering of materials.

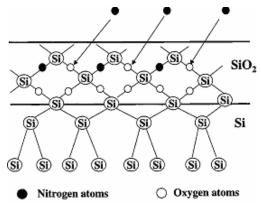

## 3. Brief history of high-k dielectric development

To overcome gate leakage problems and extend the usefulness of SiO<sub>2</sub>-based dielectric, incorporation of nitrogen into SiO<sub>2</sub> has been adopted. There are several ways to introduce nitrogen into SiO<sub>2</sub>, such as post deposition annealing in nitrogen ambient and forming a nitride/oxide stack structure. By incorporating nitrogen into SiO<sub>2</sub>, it not only increases the dielectric constant but also acts as a better barrier against boron penetration. In addition, a nitride/oxide stack structure maintains the benefits of good interface quality between the oxide and substrate [13, 14], as schematically shown in Fig. 9.

Despite the immense development with SiO<sub>2</sub>, these oxynitrides still have low k values and so a relatively thick layer is required to prevent direct tunneling current. Therefore, alternative materials with a higher k than  $SiO_2$  (3.9) are needed to achieve the required capacitance without tunneling currents [15]. Oxides of group II, III, IV such as Al<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, Sc<sub>2</sub>O<sub>3</sub> and some lanthanides such as  $Pr_2O_3$ ,  $Gd_2O_3$  and  $Lu_2O_3$  have been proposed. Unfortunately, these dielectrics will only last a few generations due to limitations dictated by low power applications, scalability, or serious reactions with the Si substrate. Yet, these problems are much smaller for oxides and silicates of Hf and Zr. Thus, the choice of alternative gate dielectrics has been narrowed to HfO<sub>2</sub>, ZrO<sub>2</sub> and their silicates due to their excellent electrical properties and high thermal stability in contact with Si [16]. However, another problem, namely low crystallization temperature, is associated with Hf-based and Zr-based oxides. They can easily crystallize during standard CMOS processes. These crystalline structures can increase the gate leakage by orders of magnitude and provide pathways for diffusion of dopants and dielectric breakdown. Up to date, many groups have focused on the improvement of the crystallization temperature of these oxides. Thus, elements such as N, Si, Al, Ta and La have been incorporated into these high-k oxides. Hf-based oxides are preferred over Zr-based oxides for its relative higher crystalline temperature.

Fig. 9. Schematic showing incoming nitrogen radicals replace oxygen atoms to form Si-N bonds [17].

# 4. Latest development in Hf-based high-k oxides

## 4.1 Fabrication methods

Hf-based High-k dielectric oxides have replaced conventional SiO<sub>2</sub> as the gate dielectric in sub-0.1 µm complementary metal-oxide-semiconductor devices [18, 19]. The fabrication technology of Hf-based high-k ultrathin dielectrics has been developed very quickly. Overall, the techniques can be categorized into two major approaches based on the reaction mechanism during preparation, namely CVD (chemical vapor deposition) and PVD (Physical Vapor Deposition) processes. CVD-based approaches include metal-organic chemical vapor deposition (MOCVD) [20], plasma-enhanced chemical vapor deposition (PECVD) [21], atomic-layer chemical vapor deposition (ALCVD) [22], photo-assisted CVD synthesis [23] and so on. These growth methods provide more flexibility and have relatively low cost. Among them, ALCVD is considered particularly promising, since this is the only feasible method to control the thickness down to the nanometer range and layer-by-layer composition of the metal oxide ultrathin film [24].

# 4.2 Doping of Hf-based high-k oxides

Crystallization of pure HfO<sub>2</sub> occurs at only about 400–450 °C causing grain boundary leakage current and nonuniformity of the film thickness [25]. As a result, impurities such as O, B, and P can penetrate the grain boundaries during high temperature postprocessing. It causes equivalent oxide thickness (EOT) scaling and reliability concerns when Hf-based high-k ultrathin gate oxides are integrated into high temperature CMOS processes [26].

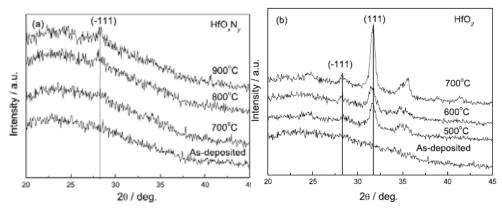

Recently, nitrogen incorporation has been extensively investigated in the field of high-k thin films [27, 28]. Nitrogen introduction into  $HfO_2$  films has significantly improved the electric properties as well as crystallinity [29, 30]. On the contrary, nitrogen doping leads to decreased band gap. This is because it adds N 2p states which lie above the O 2p states in the free atoms and so the VB is raised and the CB is reduced due to the interaction between the nonbonding Hf 5d states and adjacent O and N states. The delocalized Hfd-Np bonding states contribute an indirect band gap  $E_g$  of 1.8 eV, which is smaller than the Op-Hfd band gap of larger than 5.8 eV [31, 32]. Despite the disadvantages, the introduced nitrogen can suppress the growth of microstructure and interfacial layer. When N is added to HfO<sub>2</sub>, it is expected to distort the equilibrium of the lattice and produce disordered states. Choi et al. have demonstrated that adding nitrogen results in the reduction of the mobility of Hf and O atoms as well as increase in the nucleation temperature and consequently the crystalline temperature [33, 34]. All these indicate that nitrogen acts as a crystallization inhibitor and causes an increase in the crystallization temperature in Hf-based gate dielectrics (Fig. 10).

The interfacial layer between the high-k dielectrics and Si substrate is one of the key factors determining the performance and reliability of a MOS transistor. Hence, it is extremely crucial to fabricate a SiO<sub>2</sub>/Si like interface. From this viewpoint, a SiO<sub>2</sub> interfacial layer is often grown between Hf-based oxide and Si by thermal oxidation. However, this HfO<sub>2</sub>/SiO<sub>2</sub> gate dielectric stack usually introduces an additional EOT increase due to the low k SiO<sub>x</sub> interfacial layer. In order to solve this problem, addition of Si into Hf-based oxide to form Hf silicate may be a plausible means. Besides improvement in the interface quality, incorporation of Si into Hf-based oxides can also foster the formation of amorphous or near-amorphous structures [36, 37]. A negative effect is the reduction in the k value. The k value decreases inversely with increasing Si concentration in Hf-based oxides. When the Si content approaches 100% (alternatively, Si-based oxide), the k value comes close to the lowest value of 3.9. Accordingly, the Si content must be selected to keep a balance between gains and defects.

Fig. 10. XRD spectra for the  $HfO_2$  and  $HfO_xN_y$  films: (a) as-deposited and  $HfO_xN_y$  films annealed at different temperatures and (b) as-deposited and  $HfO_2$  films annealed at different temperatures [35].

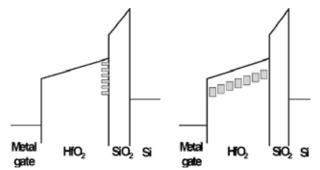

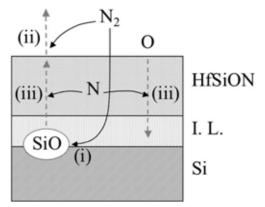

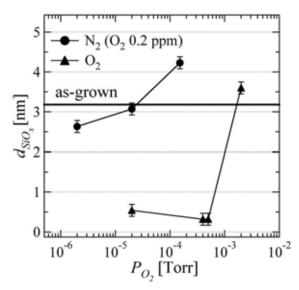

HfSiON is thermally stable compared to  $HfO_2$  due to the Si-N bonds that are created by the nitridation step, and thus HfSiON has the potential for implementation in a conventional gate-first process with high temperature activation annealing. By using nitrogenincorporated HfSiO films, both the oxidation and reduction reactions can be suppressed in the annealing process at a proper partial pressure of N<sub>2</sub> gas. The N<sub>2</sub> gas suppresses only the reduction reaction, while nitrogen atoms incorporated in the dielectrics suppress both oxidation and reduction reactions, greatly improving the electrical characteristic of Hf-based high-k dielectrics [38]. Fig. 11 schematically shows the mechanism of the suppression of reaction and the results of suppression of interfacial layer growth can be seen in Fig. 12.

Many groups have reported that the crystallization temperature of HfO<sub>2</sub> (400–450 °C) can be increased by incorporation of  $Al_2O_3$  forming an HfAlO alloy. Zhu et al. [39] have shown that Al inclusion in HfO<sub>2</sub> significantly increases the crystallization temperature. At an Al content of 31.7%, the crystallization temperature is about 400-500 °C higher than that without Al.

Fig. 11. Schematic of the mechanism for the suppression of reaction.  $N_2$  ambient gas can suppress (i) SiO formation and (ii) SiO desorption. Nitrogen atoms in the dielectric film can suppress (iii) SiO and O diffusion [38].

Fig. 12. SiO<sub>2</sub> equivalent thickness of dielectric films as a function of O<sub>2</sub> partial pressure (PO<sub>2</sub>). These thicknesses were calculated from the peak-area ratio of the Si-oxide to the Si substrate, regarding the Si-oxide component as SiO<sub>2</sub> for simplicity. A straight line at around 3.2 nm denotes the thickness of the as-grown sample [38].

This additional Al increases the band gap of the dielectrics from 5.8 eV for HfO<sub>2</sub> without Al to 6.5 eV for HfAlO with 45.5% Al but reduced dielectric constant from 19.6 for HfO2 without Al to 7.4 for Al<sub>2</sub>O<sub>3</sub> without Hf. Considering the factors including the crystallization temperature, band gap, and dielectric constant, they conclude that the optimum Al concentration is about 30% for conventional CMOS gate processing technology. Moon et al. [40] have presented the similar trend in the change of the electrical and structural properties due to the Al incorporation. Their results suggest that the HfAlO film with 10% Al<sub>2</sub>O<sub>3</sub> shows a great improvement in thermal stability and significant reduction of interfacial layer growth during subsequent thermal processes while maintaining a high k value ( $\sim$ 19), leading to reduction in the leakage current by around 2 orders of magnitude compared to pure HfO<sub>2</sub>. The HfAlO film also has good compatibility with the gate electrode in high temperature annealing process (Fig. 13). Bae et al. [41] have pointed out that while Al doping significantly increases the crystallization temperature in HfO<sub>2</sub> to up to 900 °C and improves its thermal stability, it also introduces negative fixed oxide charges due to Al accumulation at the HfAlO-Si interface, resulting in mobility degradation. The effects of Al concentration on the crystallization temperature, fixed oxide charge density, and mobility degradation in HfAlO have been characterized and correlated. In spite of these analyses, there are still a lot of issues to be settled in order to maximize the performance of the materials.

On account of the good thermal stability and electrical characteristics, HfTaO gate dielectrics have attracted attention. Incorporation of Ta into HfO<sub>2</sub> enhances the crystallization temperature dramatically while keeping a high k value of ~17 [42]. Compared to HfO<sub>2</sub> gate dielectrics, HfTaO also has the advantages of much lower charge trapping as well as BTI degradation and increased channel mobility [43]. Yu et al. [44] have confirmed that HfTaO

Fig. 13. XTEM images of HfO<sub>2</sub> and HfAlO after 700 °C in-situ PDA treatment. HfAlO layer remains amorphous while HfO<sub>2</sub> is crystallized. Both films were deposited at 400 °C without surface nitridation [40].

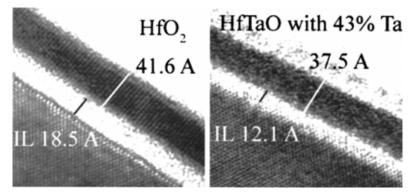

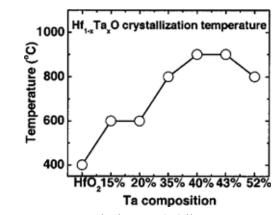

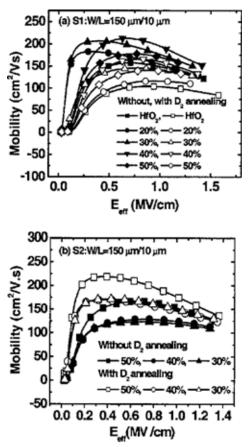

with 43% Ta remains amorphous even after annealing at 950 °C for 30 s, and the formation of low-k interfacial layer is reduced (Fig. 14). The results indicate good interface properties between the HfTaO and Si substrate and sufficiently suppressed boron penetration behavior in the HfTaO film. The negligible flat-band voltage shift in HfTaO with 43% Ta film is observed and attributed to its amorphous structure after device fabrication. It also contributes to the improvement in performance and reliability of the devices. Zhang et al. [45] have found that HfTaO with 40% Ta exhibits the highest crystallization temperature of 900 °C, while 35% and 52% HfTaO films show crystallization temperature of 800 °C (Fig. 15). The results demonstrate that HfTaO N-MOSFETs possess higher electron mobility than controlled HfO<sub>2</sub> devices. Among them, the transistors with 40% Ta doped HfTaO as the gate dielectrics have the highest electron mobility (Fig. 16).

Fig. 14. TEM images of HfO<sub>2</sub> and HfTaO with 43% Ta after PDA at 700 °C for 40 s and activation annealing at 950 °C for 30 s. Pure HfO<sub>2</sub> film is fully crystallized whereas the HfTaO with 43% Ta film remains amorphous [44].

Fig. 15. Crystallization temperature of HfTaO with different Ta composition measured by XRD with incident angle of x ray: 3° [45].

Fig. 16. Effective mobility of HfTaO N-MOSFETs (a) without and (b) with D<sub>2</sub> annealing [45].

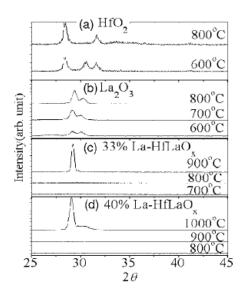

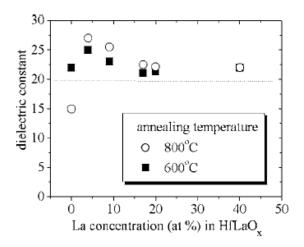

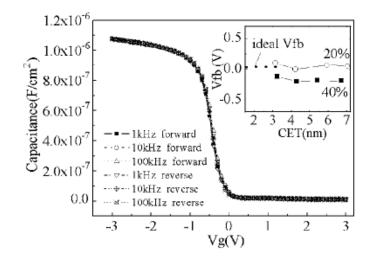

In addition, some rare earth elements such as La can also improve the characteristics of Hfbased high-k dielectrics. Introduction of La<sub>2</sub>O<sub>3</sub> into HfO<sub>2</sub> causes an increase in the crystallization temperature (Fig. 17). Furthermore, unlike other Hf-based amorphous materials such as HfSiO<sub>x</sub> or HfAlO<sub>x</sub>, the permittivity of HfLaO<sub>x</sub> still yields a high k value (>20) [ 46] (Fig. 18). Besides, HfLaO also has the advantages of much lower charge trapping as well as BTI degradation and increased channel mobility. In addition, varying the La concentrations in the TaN/HfLaO or HfN/HfLaO gate stack can effectively tune the metal work function for N-MOSFETs [43]. In the capacitance-voltage curve of metal oxide semiconductor capacitor, Yamamoto et al. [46] have shown that the HfLaO<sub>x</sub> dielectric film exhibits very small degradation in both the interface and bulk properties, as shown in Fig. 19. A very low fixed charge density in HfLaO<sub>x</sub> films is demonstrated from a very small film thickness dependence on the flatband voltage in their study.

Fig. 17. XRD spectra of 30 nm films of (a)  $HfO_2$ , (b)  $La_2O_3$ , (c) 33%  $La-HfLaO_x$ , and (d) 40% La-HfLaOx annealed at various temperatures.  $HfO_2$  and  $La_2O_3$  films crystallize under 600 °C. On the other hand, 40% La-HfLaOx film remains amorphous after 900 °C annealing [46].

An et al. [47] have synthesized ultrathin HfO<sub>2</sub> and HfLaO<sub>x</sub> films with La/(Hf+La) ratios of 42%, 57%, and 64% by an atomic layer deposition process. By measuring the leakage current at different temperatures, they propose that the conduction mechanism of HfO<sub>2</sub> and HfLaO<sub>x</sub> films follow the Poole–Frenkel emission model under the gate injection condition. They have also demonstrated that the intrinsic trap energy levels are 1.42, 1.34, 1.03, and 0.98 eV in the HfLaO<sub>x</sub> samples with La/(Hf+La) ratios of 0%, 42%, 57%, and 64%, respectively, showing a decreasing behavior as the La content is increased (Fig. 20).

Fig. 18. Dielectric constants of  $HfLaO_x$  film as a function of La concentrations. The dielectric constants are determined by MIM capacitors for the samples with La concentrations of 0%, 4%, 9%, and 17%. For 20% and 40%, CET vs physical thickness plots were used [46].

Fig. 19. C-V characteristics of Au/40% La–HfLaO<sub>x</sub>/p-Si MOS capacitor annealed at 600 °C. The film thickness was 8.4 nm. It shows very small hysteresis and frequency dispersion. The inset in the upper right shows the flatband voltages of Au/20% La–HfLaO/p-Si or 40% La–HfLaO/p-Si MOS [46].

Fig. 20. ln(J/E) vs 1/T plots measured at various applied electric fields for (a) HfO<sub>2</sub> and (b) Hf<sub>0.36</sub>La<sub>0.64</sub>O<sub>x</sub> films, and (c) trap energy level as a function of  $E^{1/2}$  for both samples [47].

From the above results, it can be easily inferred that  $HfLaO_x$  is a potential dielectric material for amorphous high-k gate insulator in further advanced complementary metal oxide semiconductor (CMOS) devices.

# 5. Conclusion

This chapter succinctly reviews the motivation to replace traditional  $SiO_2$  gate dielectrics, requirements of high-k dielectrics, brief history of high-k materials development, and latest development in Hf-based high-k dielectrics. In order to improve the performance of CMOS devices, Hf-based gate layers are being integrated into MOSFETs to achieve low leakage current. Excellent gate transistors with improved performance based on Hf-based gate dielectrics as the insulating layers are expected. Although much progress has been made in fabricating novel gate dielectrics, investigation of these Hf-based high-k gate dielectrics

continues to be exciting and the final target has not yet been reached. There is still room for development and many issues need better understanding.

## 6. Acknowledgments

This work was jointly supported by National Natural Science Foundation of China (Grant No. 50802005), Program for New Century Excellent Talents in University (NCET-08-0035), Ph.D. Program Foundation of Ministry of Education of China (Grant No. 200800061055), and Hong Kong Research Grants Council (RGC) General Research Funds (GRF) No. CityU 112608.

### 7. References

- Moore, G.E. (1975). Progress in digital integrated electronics. in Electron Devices Meeting, 1975 International.

- [2] Chau, R.; Datta, S.; Doczy, M.; Doyle, B.; Kavalieros J.; & Metz M. (2004). High-k/Metal-Gate Stack and Its MOSFET Characteristics, vol. 25, pp. 408-410, IEEE Electron Device Lett.

- [3] Robertson, J. (2006). High dielectric constant gate oxides for metal oxide Si transistors, vol. 69, pp. 327-396, Rep. Prog. Phys.

- [4] Plummer, J. D. & Griffin, P. B. (2001). Material and process limits in silicon VLSI technology, pp. 240-258, Proc. IEEE, 2001.

- [5] Robertson, J. (2000). Band offsets of wide-band-gap oxides and implications for future electronic devices, vol. 18, pp. 1785-1791, J. Vac. Sci. Technol. B.

- [6] Kingon, A. I.; Kingon, A. I.; Maria, J. P. & Streiffer, S. K. (2000). Alternative dielectrics to silicon dioxide for memory and logic devices, vol. 406, pp.1032-1038, Nature.

- [7] Robertson, J. & Chen, C. W. (1999). Schottky barrier heights of tantalum oxide, barium strontium titanate, lead titanate, and strontium bismuth tantalate, vol. 74, pp. 1168-1170, Appl. Phys. Lett.

- [8] Copel, M.; Gribelyuk, M. & Gusev, E. (2000). Structure and stability of ultrathin zirconium oxide layers on Si(001), vol. 76, pp. 436-438, Appl. Phys. Lett.

- [9] Schlom, D. G. & Haeni, H. J. (2002). A thermodynamic approach to selecting alternative gate dielectrics, vol. 27, pp. 198-204, MRS Bull.

- [10] Stemmer, S.; Li. Y; Foran, B.; Lysaght, P. S.; Streiffer, S. K.; Fuoss, P. & Seifert, S. (2003). Grazing-incidence small angle x-ray scattering studies of phase separation in hafnium silicate films, vol. 83, pp. 3141-3143, Appl. Phys. Lett.

- [11] Wilk, G. D.; Wallace, R.M. & Anthony, J.M. (2001). High-kappa gate dielectrics: Current status and materials properties considerations, vol 89, pp. 5243-5275, Journal of Applied Physics.

- [12] Robertson, J. (2005). Interfaces and defects of high-K oxides on silicon, vol. 49, pp. 283-293, Solid State Electron.

- [13] Buhrman, R. A. & Ellis, K. A. (1999). Time-dependent diffusivity of boron in silicon oxide and oxynitrides, vol. 74, pp. 967-969, Appl. Phys. Lett.

- [14] Kumar, K.; Chou, A. L.; Lin, C.; Choudhury, P. & Lee, J. C. (1997). Optimization of sub 3 nm gate dielectrics grown by rapid thermal oxidation in a nitric oxide ambient, vol. 70, pp. 384-386, Appl. Phys. Lett.

- [15] Kizilyalli, I.C.; Huang, R.Y.S. & Roy, R.K. (1998). MOS transistors with stacked SiO2-Ta2O5 -SiO2 gate dielectrics for giga-scale integration of CMOS technologies, vol. 19, pp. 423-425, IEEE Electron. Device Lett.

- [16] Qi, W. J.; Nieh, R.; Lee, B. H.; Kang, L. G.; Jeon, Y.; Onishi, T.N. K.; Banerjee, S. & Lee, J.C. (1999). MOSCAP and MOSFET characteristics using ZrO2 gate dielectric deposited directly on Si, pp. 145-148, Tech. Dig. Int. Electron. Device. Meet.

- [17] Alshareef, H. N.; Niimi, H.; Varghese, A.; Bevan, M.; Kuan, R.; Holt, J.; Tiner, P. & Khamankar, R. (2005). Intrinsic reoxidation of microwave plasma-nitrided gate dielectrics, vol. 86, pp. 132901-3, Appl. Phys. Lett.

- [18] G.Pant, A. G.; Kim, M. J.; Wallace, R.M.; Quevedo-Lopez, M. A. & Kirsch, P. D. (2006). Effect of thickness on the crystallization of ultrathin HfSiON gate dielectrics, vol. 88, pp. 032901-3 Appl. Phys. Lett.

- [19] Kita, K.; Kyuno, K. & Toriumi, A. (2005). Permittivity increase of yttrium-doped HfO2 through structural phase transformation, vol. 86, pp. 102906-3, Appl. Phys. Lett.

- [20] Lu, X.-b.; Liu, Z.-G.; Wang, Y.-P.; Yang, Y.; Wang, X.-P.; Zhou, H.-W. & Nguyen, B.-Y. (2003). Structure and dielectric properties of amorphous LaAlO[sub 3] and LaAlO[sub x]N[sub y] films as alternative gate dielectric materials, vol. 94, pp. 1229-1234, J. Appl. Phys.

- [21] Kim, H. & McIntyre, P. C. (2002). Spinodal decomposition in amorphous metal-silicate thin films: Phase diagram analysis and interface effects on kinetics, vol. 92, pp. 5094-5096, J. Appl. Phys.

- [22] Biercuk, M.J.; Monsma, D. J.; Marcus, C. M.; Becker, J. S.; Gordon, R. G. (2003). Lowtemperature atomic-layer-deposition lift-off method for microelectronic and nanoelectronic applications, vol. 83, pp. 2405-2407, Appl. Phys. Lett.

- [23] Tokita, K & Okada, F. (1996). Growth of metal oxide thin films by laser-induced metalorganic chemical vapor deposition, vol. 80, pp. 7073-7075, J. Appl. Phys.

- [24] Hausmann, D.; Becker, J.; Wang, S. & Gordon, R. G. (2002). Rapid Vapor Deposition of Highly Conformal Silica Nanolaminates, vol. 298, pp. 402-406, Science.

- [25] Zhu, W.; Ma, T. P.; Tamagawa, T.; Di, Y.; Kim, J.; Carruthers, R.; Gibso, M. & Furukawa, T. (2001). pp. 4.1, Tech. Dig. Int. Electron Device Meet.

- [26] Choi, C.H.; Rhee, S. J.; Jeon, T.S.; Lu, N.; Sim, J. H.; Clark, R.; Niwa, M. & Kwang, D. L. (2002). pp. 865, Tech. Dig. Int. Electron Device Meet.

- [27] Chen, P.; Bhandari, H. B. & Klein, T. M. (2004). Effect of nitrogen containing plasmas on interface stability of hafnium oxide ultrathin films on Si(100), vol. 85, pp. 1574-1576, Appl. Phys. Lett.

- [28] Choi, C.H.; Jeon, T.S.; Clark, R. & Kwong, D.L. (2003). Electrical properties and thermal stability of CVD HfOxNy gate dielectric with poly-Si gate electrode, vol. 24, pp. 215-217, IEEE Electron Device Lett.

- [29] Choi, K. J.; Kim, J. H. & Yoon, S. G. (2004) Characterization of HfO2 and HfOxNy Gate Dielectrics Grown by PE Metallorganic CVD with a TaN Gate Electrode, vol. 151, pp. G262-G265, J. Electrochem. Soc.

- [30] Kang, C. S.; Cho, H. J.; Onishi, K.; Nieh, R.; Choi, R.; S.Gopanlan, S.K.; Han, J.H. & Lee, J. C. (2002). Bonding states and electrical properties of ultrathin HfOxNy gate dielectrics, vol. 81, pp. 2539-2541, Appl. Phys. Lett.

- [31] Kroll, P. (2003). Hafnium Nitride with Thorium Phosphide Structure: Physical Properties and an Assessment of the Hf-N, Zr-N, and Ti-N Phase Diagrams at High Pressures and Temperatures, vol. 90, pp. 125501, Phys. Rev. Lett.

- [32] Lim, S. G.; Kriventsov, S.; Jackson, T. N.; Haeni, J. H.; Schlom, D. G.; & Balbashov, A. M. (2002). Dielectric functions and optical bandgaps of high-K dielectrics for metal-oxidesemiconductor field-effect transistors by far ultraviolet spectroscopic ellipsometry, vol. 91, pp. 4500, J. Appl. Phys.

- [33] Cho, M. H.; Roh, Y. S.; Whang, C. N.; Jeong, K.; Choi, H. J.; Nam, S. W.; Ko. D. H.; Lee, J. H.; Lee, N. I. & Fujihara, K. (2002). *Dielectric characteristics of Al2O3-HfO2 nanolaminates on Si(100)*, vol. 81, pp. 1071-1073, Appl. Phys. Lett.

- [34] K.J.Choi, J.H.Kim, J. H.; Yoon, S.G. & Shin, W.C. (2004) Structural and electrical properties of HfOxNy and HfO2 gate dielectrics in TaN gated nMOSCAP and nMOSFET devices, vol. 22, pp. 1755-1758, J. Vac. Sci. Technol. B.

- [35] He, G.; Fang, Q. & Zhang, L. D. (2006). vol. 9, pp. 870, Mater. Sci. Semicon. Proc.

- [36] Hu, J.C.; Yang, H.; Kraft, R.; Rotondaro, A.L.P.; Hattangady, S.; Lee, W.W.; Chapman, R.A.; Chao, C.-P.; Chatterjee, A.; Hanratty, M.; Rodder, M. & Chen, I.-C. (1997). *Feasibility of using W/TiN as metal gate for conventional 0.13 μm CMOS technology and beyond*, pp. 825-828, Tech. Dig. Int. Electron Devices Meet.

- [37] ITRS. (2003). ITRS Roadmap.

- [38] Kamada, H.; Tanimura, T.; Toyoda, S.; Kumigashira, H.; Oshima, M.; Liu, G. L.; Liu, Z. & Ikeda K. (2008). Control of oxidation and reduction reactions at HfSiO/Si interfaces through N exposure or incorporation, vol. 93, pp. 212903-3, Appl. Phys. Lett.

- [39] Zhu, W. J.; Tamagawa, T.; Gibson, M.; Furukawa, T. & Ma, T. P. (2002). Effect of Al inclusion in HfO<sub>2</sub> on the physical and electrical properties of the dielectrics, vol. 23, pp. 649-651, IEEE Electron Device Lett.

- [40] Joo, M. S.; Cho, B. J.; Yeo, C. C.; Chan, S. H.; Whoang, S. J.; Mathew, S.; Kanta, B. L. & Balasubramanian, N. (2003). Dim-Lee, Kwong Formation of hafnium-aluminum-oxide gate dielectric using single cocktail liquid source in MOCVD process, vol. 50, pp. 2088-2094, IEEE Transactions on Electron Devices.

- [41] Bae, S. H.; Lee, C. H.; Clark, R. & Kwong, D. L. (2003). *MOS characteristics of ultrathin CVD HfAlO gate dielectrics*, vol. 24, pp. 556-558, IEEE Electron Device Lett.

- [42] Lu, X.-b.; Maruyama, K. & Ishiwara, H. (2008). Characterization of HfTaO films for gate oxide and metal-ferroelectric-insulator-silicon device applications, vol. 103, pp. 044105-5, J. Appl. Phys.

- [43] Li, M.-F.; Zhu, C.-X; Shen, C. Y.; Xiong, F. F.; Yuan, P.; Yeo, Y. C.; Chin, A.; Kwong, D.-L.; Wang, S. H.; Du, A. Y. & Samudra, G. (2006). New Insights in Hf Based High-k Gate Deielectrics in MOSFETs, vol. 1, pp. 717-730, ECS Transactions.

- [44] Yu, X.-F.; Zhu, C.-X.; Li, M. F.; Chin, A.; Du, A. Y.; Wang, W. D. & Kwong, D.-L. (2004). Electrical characteristics and suppressed boron penetration behavior of thermally stable HfTaO gate dielectrics with polycrystalline-silicon gate, vol. 85, pp. 2893-2895, Appl. Phys. Lett.

- [45] Zhang, M.H.; Rhee, S. J.; Kang, C. Y.; Choi, C. H.; Akbar, M. S.; Krishnan, S. A.; Lee, T.; Ok, I. J.; Zhu, F.; Kim, H. S. & Lee, J. C. (2005). *Improved electrical and material characteristics of HfTaO gate dielectrics with high crystallization temperature*, vol. 87, pp. 232901-3, Appl. Phys. Lett.

- [46] Yamamoto, Y.; Kita, K.; Kyuno, K. & Toriumi, A. (2006). Structural and electrical properties of HfLaO[sub x] films for an amorphous high-k gate insulator, vol. 89, pp. 032903-3, Appl. Phys. Lett.

- [47] An, C.-H.; Lee, M. S.; Choi, J.-Y. & Kim, H. (2009). Change of the trap energy levels of the atomic layer deposited HfLaO[sub x] films with different La concentration, vol. 94, pp. 262901-3, Appl. Phys. Lett.